در سال 1965 آقای مور پیش بینی کرد که تعداد ترانزیستور های روی یک تراشه هر دو سال یکبار دو برابر می شود. اما این کاهش ابعاد ترانزیستور ها به زودی به پایان خواهد رسید. به عنوان مثال بخش هایی از ترانزیستورها تنها به اندازه چند اتم ضخامت دارند. بنابراین وقتی ابعاد این بخش ها به یک یا دو اتم برسند کاهش ابعاد ترانزیستورها متوقف خواهد شد. بنابراین ناچاریم به یک فناوری جدید به نام فناوری نانو رو بیاوریم. کوچک سازی ابعاد همچنین می تواند سبب کوچک تر شدن ابعاد مدارات، قیمت پایین تر، سرعت بالا تر و توان مصرفی پایین تر شود. پیش بینی ها توسط ITRS نشان می دهد که کوچک سازی CMOS ها در حدود سال 2018 با رسید به عرض کانال 20nm به پایان خواهد رسید. بزرگترین مشکل برای کاهش ابعاد ترانزیستورها، مسائل اقتصادی مربوط به آنهاست. با وجودیکه این فرایند امکان ساخت مدارات و سیستم های قابل اطمینان را به ما می دهد، کاهش ابعاد، تولید ماسک های قابل اطمینان را بسیار گران می کند. به هر حال دو مشکل اساسی وجود دارند که نیاز به حل آنهاست. اول هزینه های سرسام آور و دوم محدودیت های اندازه فیزیکی. راه حل این مشکلات استفاده از فناوری نانو است. بطور مثال سیم ها، دیودها و ترانزیستور ها و... می توانند با این تکنولوژی کوچک سازی شوند.

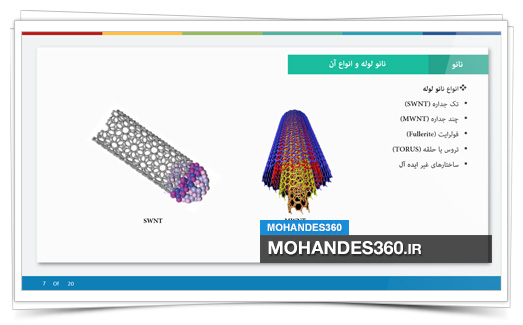

در این مجموعه فایل به بررسی ترانزیستور های نانو لوله کربنی CNTFET پرداخته شده و همچنین کلیه فایل های مربوط به پروژه فایل اصلی پاورپوینت، رفرنس ها و مقالات و بخضی از فایل های ترجمه شده، خلاصه گزارش و دو پایان نامه در این خصوص در این مجموعه قرار گرفته است. فهرست مطالب: مقدمه:قانون مورموانع کاهش ابعاد ترانزیستورهای سیلیکونی نانو:نانو لوله و انواع آنقوس الکتریکی، CVD و تبخیر لیزریساختارنمودار جریان نسبت به VGS و VDS مقایسه:مقایسه با دیگر افزاره ها با کانال حدود 10 نانومتر شبیه سازی:متدهای شبیه سازینرم افزار نتیجه گیری:ویژگی های و چالش های نانو لوله کربنینتیجه گیری

:: برچسبها:

CNTFET ,

JL_CNTFET ,

CNT ,

ترانزیستور نانولوله کربنی ,

نانو لوله ,

نانوسیم ,

قانون مور ,

:: بازدید از این مطلب : 235

|

امتیاز مطلب : 0

|

تعداد امتیازدهندگان : 0

|

مجموع امتیاز : 0